مداری که در ذهن شما به عنوان طراح و پیادهساز دیجیتال وجود دارد باید به نحوی برای FPGA توصیف شود.

این کار عملا توسط نرمافزارهای مخصوصی که برای این هدف طراحی شدهاند انجام میشود.

اما سوال اساسی در ذهن بسیاری از افرادی که به تازگی وارد دنیای پیادهسازی با FPGA شدهاند این که چطور طرح مدار دیجیتالی را که در ذهن دارند برای نرمافزار پیادهسازی توصیف کنند.

در این برنامه ویدئویی، روشهای توصیف مدارات دیجیتال برای نرمافزارهای پیادهسازی دیجیتال با FPGA را به شما توضیح میدهم و همچنین روش اصلی را که در عمل و در پروژههای حرفهای از آن استفاده میشود معرفی میکنم.

More...

به طور کلی، دو روش برای توصیف مدارات دیجیتال برای نرمافزارهای پیادهسازی وجود دارد:

در این برنامه در مورد مزایا و معایب استفاده از هر کدام از این دو روش صحبت خواهم کرد و نهایتا توضیح خواهم داد که در پروژههای حرفهای از کدام یک از این روشها استفاده میشود.

در ادامه این ویدئو، همچنین به صورت مقدماتی در مورد زبان VHDL و مفاهیم مهم آن صحبت خواهم کرد و بخشهای اصلی آن را به کمک یک مثال بسیار ساده معرفی میکنم.

برای آشنایی بیشتر با زبان VHDL، این برنامه ویدئویی را ببینید...

ویدئو یا متن؟

محتوای این برنامه آموزشی، به دو صورت ویدئو و متن آماده شده است. اگر علاقمند به یادگیری این مطلب به صورت ویدئویی هستید، ویدئوی زیر را ببینید و اگر ترجیح میدهید آن را به صورت متن مطالعه کنید، ادامه این مطلب را بخوانید.

برای دانلود نسخه با کیفیت این ویدئو، روی دکمه زیر کلیک کنید:

در این برنامه میخواهم در مورد چگونگی توصیف یک مدار دیجیتال برای FPGA صحبت بکنم.

اگر از برنامههای گذشته به یاد داشته باشید، گفتم در FPGA، مدارها به کمک منابع دیجیتالی موجود در آن پیادهسازی میشوند.

اما سوالی که پیش میآید این است که در ابتدا چطور یک مدار دیجیتال را برای FPGA توصیف بکنیم؟

قبل از اینکه به این پرسش پاسخ دهیم، ببینیم هنگامی که با پردازندهها سر و کار داریم چطور سیستم و ایدهی طرح را برای آنها معرفی میکنیم.

پیادهسازی در پردازندهها

وقتی با پردازنده کار میکنیم به کمک دستورات برنامهنویسیای که از پیش برای آن پردازنده تعریف شده است، میتوانیم یک الگوریتم را در آنها پیادهسازی کنیم.

بنابراین، در پردازندهها زبان برنامهنویسی ابزاری است که به کمک آن ایدهای را که در ذهن داریم میتوانیم به پردازنده معرفی کنیم.

اما این موضوع در مورد FPGAها به چه صورت است؟

چطور میتوانیم مدار دیجیتالی که در ذهن داریم، یا روی کاغذ طراحی کردهایم، را برای FPGAها توصیف بکنیم.

روشهای توصیف مدار در FPGA

برای توصیف مدارها در FPGA به طور کلی دو روش وجود دارد.

روش اول استفاده از شماتیک مداری است.

در روش شماتیک مداری، شما به کمک یک نرمافزار و به کمک قطعات پایهی دیجیتالی میتوانید مدار را ترسیم و برای FPGA توصیف بکنید.

به طورمثال، میتوانید به کمک گیتهای پایه، فلیپفلاپها، بلوکهای مالتیپلکسر، انکودر، دیکودر و ... مدارهای مختلف را برای FPGA رسم و توصیف کنید.

این روش به نظر خیلی ساده میآید، ولی در عمل کاربرد چندانی ندارد.

زیرا با این روش، مدیریت و ترسیم مدارهای بزرگ در این نرمافزار تقریبا غیر ممکن است.

فرض کنید، میخواهید مداری را ترسیم کنید که از هزاران گیت و بلوکهای دیجیتالی تشکیل شده است.

اولا، ترسیم آن در صفحهی محدود مانیتور بسیار سخت است.

ثانیا، در صورت ترسیم شماتیک، اگر ایرادی در آن وجود داشت یا اگر خواستید تغییری در آن انجام دهید، این کار میتواند خیلی مشکل و تقریبا غیرممکن باشد.

گیتهای پایه برای توصیف شماتیکی مدار در FPGA

به همین دلیل برای توصیف مدارهای بزرگ در FPGA روش دیگری به اسم زبانهای توصیف سختافزاری، وجود دارد.

زبان توصیف سختافزار (HDL)

زبان توصیف سختافزار یا Hardware Description Language که به اختصار به آن HDL گفته میشود، زبانی است که در آن ساختارها و عباراتی وجود دارد که به کمک آنها میتوانیم رفتار مدار دیجیتال را توصیف کنیم.

در واقع زبان توصیف سختافزاری از دستورات تشکیل نشده است.

چون دستورات مربوط به CPU هستند.

اما همانطور که میدانید در FPGAها نه تنها CPU، بلکه در ابتدا هیچ سختافزاری که توصیفکننده و ارائهکنندهی یک قابلیت مشخص باشد وجود ندارد.

بنابراین زبان توصیف سختافزاری زبانی نیست که از دستورات تشکیل شده باشد.

بلکه در این زبان ساختارها و عباراتی وجود دارند، که اگرچه ممکن است شبیه دستورات برنامهنویسی باشند، ولی در عمل توصیفکنندهی سختافزار دیجیتال هستند.

اجازه بدهید مفهوم زبان سختافزاری را با یک مثال بیشتر توضیح دهم.

کدی را که در زیر میبینید، یک ساختار شرطی if-then-else است که در اکثر زبانهای برنامهنویسی وجود دارد.

فرض کنید این بخش یک کد به زبان مثلا C است که توسط یک پردازنده قرار است اجرا شود.

دستور if-then-else قبلا برای CPU تعریف شده است و CPU در هنگام مواجه شدن با این دستور، با توجه به مقدار C مقدار A یا B را به F منتقل میکند.

اگر C مساوی صفر باشد، A به F منتقل میشود و درغیر این صورت B به F منتقل میشود.

اما اگر فرض کنیم که این عبارات توصیفکنندهی یک سختافزار دیجیتال هستند، این عبارات چه سختافزار دیجیتالی را توصیف میکنند؟

این عبارات توصیفکنندهی یک مالتیپلکسر دو به یک هستند.

مالتیپلکسر دو به یک حاصل از کد بالا

در مالتیپلکسر دو به یک، با توجه به مقدار C یکی از ورودیهای A یا B به خروجی F منتقل میشود. همانطور که میبینید، این کد هم دقیقا این مفهوم دیجیتال را دارد معرفی و توصیف میکند.

بنابراین در این کد سختافزاری، دستوری برای اجرا در CPU وجود ندارد، بلکه یک ساختار یا یک توصیف از یک مدار سختافزاری دیجیتالی است.

زبانهای توصیف سختافزاری مختلفی در دنیا وجود دارند.

VHDL و Verilog از معروفترین و پرکاربردترین آنها هستند.

اگرچه این دو زبان در ظاهر و ساختار تفاوتهایی دارند ولی به کمک هر دو زبان میتوانید هر نوع مدار دیجیتالی را توصیف کنید.

در ادامه کمی بیشتر با زبان VHDL آشنا میشویم.

زبان VHDL

VHDL مخفف عبارت VHSIC Hardware Description Language است.

حرف V مخفف Very High Speed Integrated Circuit است.

بنابراین، به طور کل VHDL مخفف زبان توصیف سختافزاری مدارات مجتمع با سرعت خیلی زیاد است.

VHDL ابتدا توسط وزارت دفاع آمریکا ابداع شد.

در آن زمان هدف از ابداع این زبان، پیادهسازی یک سیستم دیجیتال نبود، بلکه به کمک آن زبان میخواستند مداراتی را که قبلا پیادهسازی کردهاند، مستندسازی کنند.

هدف دیگر از ابداع این زبان، انجام مدلسازیهای مدارات دیجیتال بود.

اما بعدها از این زبان برای پیادهسازی سیستمهای دیجیتال استفاده شد.

نهایتا این زبان توسط سازمان IEEE استانداردسازی شد و زبان VHDL فعلیای که ما در حال استفاده از آن هستیم، زبان استاندارد شده در سازمان IEEE است.

همانطور که گفتم زبان VHDL یک زبان برنامهنویسی نیست، بلکه زبانی است که به کمک آن میتوانیم یک طرح سختافزاری را توصیف کنیم.

اکنون میخواهیم با ساختار زبان VHDL کمی آشنا شویم.

Entity و Architecture

هر کد VHDL به طور کلی از دو بخش تشکیل شده است.

این دو بخش را به کمک شکل زیر توضیح میدهم:

بخش Entity و Architecture مدار دیجیتال

در این شکل فرض کنید که ما یک IC یا یک مدار دیجیتال داریم.

به طور کلی میتوان این مدار دیجیتال را به دو بخش تقسیم کرد:

یک بخش پایهها، پینها، یا پورتهای ورودی-خروجی هستند و بخش دیگر، مدار داخلی است.

در اصطلاحِ VHDL به پینها یا پورتهای ورودی-خروجی Entity و به مدار داخلی Architecture گفته میشود.

در بخش اول یا همان Entity، تنها کاری که ما انجام میدهیم تعریف پورتها است.

یعنی برای پورتها اسم انتخاب میکنیم و مشخص میکنیم که این پورتها ورودی، خروجی یا دو طرفه هستند.

همچنین نوع آن پورتها را هم مشخص میکنیم.

اما بخش اصلی یک کد VHDL، بخش Architecture است که میتوانیم یک مدار دیجیتال را در آن توصیف بکنیم.

توصیف تمام جمعکننده با زبان VHDL

برای آشنایی بیشتر با این زبان یک مثال را با هم بررسی میکنیم.

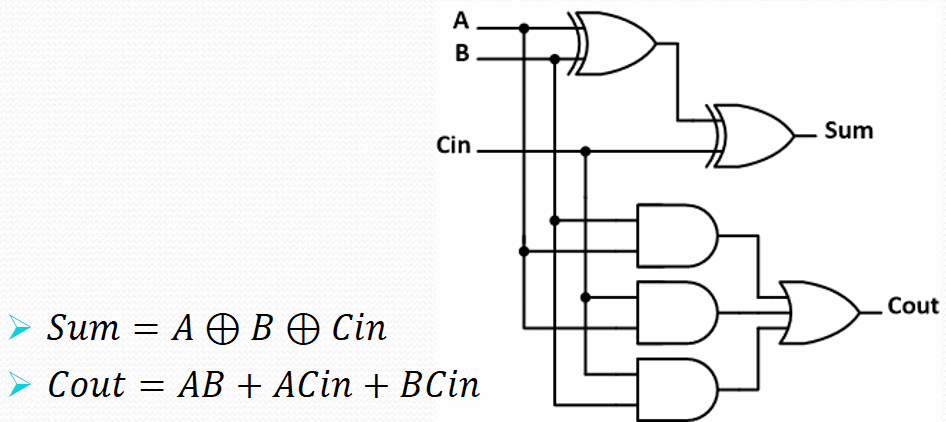

در تصویر زیر یک مدار تمام جمعکننده و توابع خروجی آن را مشاهده میکنید:

همانطور که از درس مدار منطقی به یاد دارید، یک مدار تمام جمعکننده سه ورودی B ،A و Cin را باهم جمع و Sum و Cout را تولید میکند.

توابع عبارات منطقی Sum و Cout در شکل بالا قابل مشاهده است.

برای پیادهسازی این توابع، ابتدا باید به کمک ساختار Entity، ورودی-خروجیها را معرفی کنیم و سپس در بخش Architecture مدار داخلی را توصیف بکنیم.

این مدار سه ورودی A و B و Cin و دو خروجی Sum و Cout دارد که میتوانیم به کمک ساختار Entity آن را در زبان VHDL توصیف بکنیم.

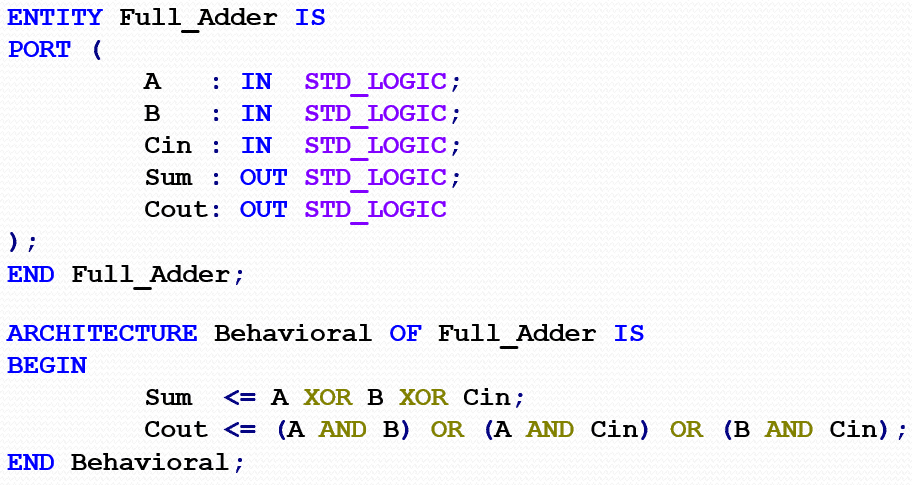

همانطور که در کد زیر ملاحظه میکنید بخش Entity با کلمه کلیدی Entity شروع میشود و پس از آن، اسم Entity قرار میگیرد، که نام آن را Full Adder گذاشتیم.

پس از اسم Entity کلمهی کلیدی IS قرار دارد که پس از این کلمه کلیدی، پورتها را معرفی میکنیم.

مثلا برای توصیف پورتِ اول، ابتدا باید اسم آن را مشخص کنیم، که ما اسم این پورت را A گذاشتیم.

سپس علامت دو نقطه (:) قرار میگیرد و پس از آن نوع ورودی یا خروجی بودن پورت تعیین میگردد.

با توجه به اینکه پورت A ورودی است، از کلمه کلیدی IN استفاده کردیم.

در نهایت هم باید نوع پورت را مشخص کنیم که از نوع STD_Logic استفاده کردیم.

در برنامههای بعدی راجع به نوع STD_Logic صحبت خواهم کرد.

حال که پورتها را تعریف کردیم نوبت توصیف مدار داخلی است که آن را به کمک ساختار Architecture معرفی میکنیم.

بخش Architecture با کلمهی کلیدی Architecture شروع میشود، سپس به ترتیب اسم Architecture، کلمهی کلیدی of، اسم Entity و کلمهی کلیدی is قرار میگیرد.

بعد از کلمهی کلیدی begin میتوانید مدار داخلی را توصیف کنید.

خوشبختانه توابع پایه مثل NOR ،NAND ،XNOR ،XOR ،NOT ،OR ،AND در زبان VHDL از قبل تعریف شدهاند.

بنابراین به کمک این توابع میتوانیم خروجی Sum و Cout را تولید کنیم.

به طور مثال تابع A XOR B XOR Cin را نوشتیم و به خروجی Sum ارجاع دادیم.

برای نسبت دادن این ترکیب منطقی به خروجی Sum، از علامت کوچکتر مساوی (=>) در این زبان استفاده میشود، که اصطلاحا به آن علامت ارجاع یا Assignment گفته میشود.البته این مثال یک مدار ساده اما کامل برای پیادهسازی مدار در زبان VHDL بود.

در این برنامه مختصرا با زبان VHDL آشنا شدیم و توانستیم یک مدار ساده اما کامل را توصیف کنیم، در برنامههای بعد دربارهی امکانات زبان VHDL و پیادهسازی مدارات پیچیدهتر، بیشتر صحبت خواهم کرد.

آیا برنامه ویدئویی توصیف مدارات دیجیتال برای FPGA برای شما مفید بود؟

لطفا نظرتان را در مورد این برنامه در پایین همین پست با دیگران به اشتراک بگذارید. همچنین با کلیک روی هر کدام از دکمههای اشتراک گذاری ابتدای این مطلب و به اشتراکگذاری آن در شبکههای اجتماعی میتوانید افراد بیشتری را در یادگیری این مطالب سهیم کنید.

بسیار عالی