بعد از اینکه یک طرح دیجیتالی را که در ذهن شما است به کمک یکی از زبانهای توصیف سختافزاری مثل VHDL یا Verilog توصیف کردید، مراحلی وجود دارد تا مدار مورد نظر شما در FPGA پیادهسازی شود.

در این برنامه ویدئویی، این مراحل هفتگانه را به شما توضیح خواهم داد تا یک دید کلی نسبت به کل فرآیند پیادهسازی مدار دیجیتال با FPGA به دست آورید.

More...

اولین مرحله پیادهسازی مدار دیجیتال با FPGA اصطلاحا ورود طرح یا design entry نام دارد که در واقع همان توصیف مدار به کمک یک زبان HDL و وارد کردن این توصیف در نرمافزار پیادهسازی مثل ISE یا ویوادو است.

برای آشنایی بیشتر با زبان VHDL، این برنامه ویدئویی را ببینید...

مراحل هفتگانه پیادهسازی مدار دیجیتال با FPGA به صورت زیر است:

- 1ورود طرح - Design Entry

- 2شبیهسازی طرح - Design Simulation

- 3سنتز طرح - Design Synthesis

- 4جانمایی طرح - Design Placement

- 5مسیریابی طرح - Design Routing

- 6ایجاد فایل پیکرهبندی - Configuration File Creation

- 7پیکرهبندی FPGA یا FPGA Configuration

در این برنامه، این هفت مرحله را که معمولا توسط نرمافزار پیادهسازی انجام میشود به علاوه وظایف اصلی شما به عنوان پیادهساز مدار دیجیتال در FPGA توضیح میدهم.

ویدئو یا متن؟

محتوای این برنامه آموزشی، به دو صورت ویدئو و متن آماده شده است. اگر علاقمند به یادگیری این مطلب به صورت ویدئویی هستید، ویدئوی زیر را ببینید و اگر ترجیح میدهید آن را به صورت متن مطالعه کنید، ادامه این مطلب را بخوانید.

برای دانلود نسخه با کیفیت این ویدئو، روی دکمه زیر کلیک کنید:

در این برنامه میخواهم درباره مراحل پیادهسازی مدار دیجیتال با FPGA صحبت کنم.

همانطور که از برنامههای قبلی به یاد دارید، درون FPGA از هزاران منبع سختافزاری مثل LUTها و منابع سیمبندی تشکیل شده است که به کمک آنها میتوانیم هر مدار دیجیتالی بزرگی را پیادهسازی کنیم.

به عبارت دیگر، با پیکرهبندی یا Configure کردن محتوای LUTها و شبکهی سوییچها میتوانیم هر نوع مداری را طراحی کنیم.

از طرف دیگر به یاد دارید که به کمک زبان HDL میتوانیم طرح دیجیتالیای که در ذهن داریم، را در یک نرمافزار برای FPGA توصیف کنیم.

اما سوالی که وجود دارد، این است که طرحی را که به عنوان یک زبان توصیف سختافزاری یا HDL توصیف کردیم، چطور و با انجام چه مراحلی به مرحلهی پیکرهبندی LUTها در FPGA برسانیم.

مراحل پیکرهبندی FPGA

برای این کار هفت مرحله باید انجام شود که آنها را مرحله به مرحله برای شما توضیح خواهم داد.

۱ - ورود طرح

اولین مرحله برای پیادهسازی یک طرح دیجیتال ورود طرح است.

ورود طرح یعنی اینکه طرح دیجیتالی مورد نظر، به کمک یکی از زبانهای توصیف سختافزاری VHDL یا Verilog، در یک Editor متن نوشته شود.

این مرحله یعنی مرحلهی ورود طرح، در عمل طولانیترین مرحلهی پیادهسازی است.

در این مرحله هر چه شما به زبان VHDL یا Verilog مسلطتر باشید و هر چه با ساختار FPGA بیشتر آشنا باشید و بهتر بتوانید منابع درون آن را به کار بگیرید، میتوانید نتیجهی بهتری به دست بیاورید.

از طرف دیگر هر چه دانش عمومی شما در طراحی دیجیتال بیشتر باشد، میتوانید مدارات بهینهتری را طراحی کنید.

۲ - شبیهسازی

مرحلهی دوم شبیهسازی طرح است.

بعد از اینکه شما طرح را به کمک یکی از زبانهای توصیف سختافزاری پیادهسازی کردید، باید از صحت عملکرد آن هم مطمئن شوید.

اینکار را میتوانید به کمک شبیهسازی انجام دهید.

در شبیهسازی معمولا به مدار یک سری ورودیهای مشخص را اعمال میکنیم و انتظار داریم که خروجیهای مشخص داشته باشیم.

با مقایسهی خروجیهای مداری که طراحی کردهاید، و خروجیهای مطلوب میتوانید متوجه شوید که مدار مورد نظر را به صورت صحیح پیادهسازی کردهاید یا خیر.

۳ - سنتز

مرحلهی سوم یکی از مهمترین مراحل در پیادهسازی یک مدار دیجیتال با FPGA است.

این مرحله سنتز طرح نام دارد

به طور کلی سنتز در پیادهسازی، تبدیل از یک توصیف سختافزاری سطح بالا به توصیف سطح پایینتر است.

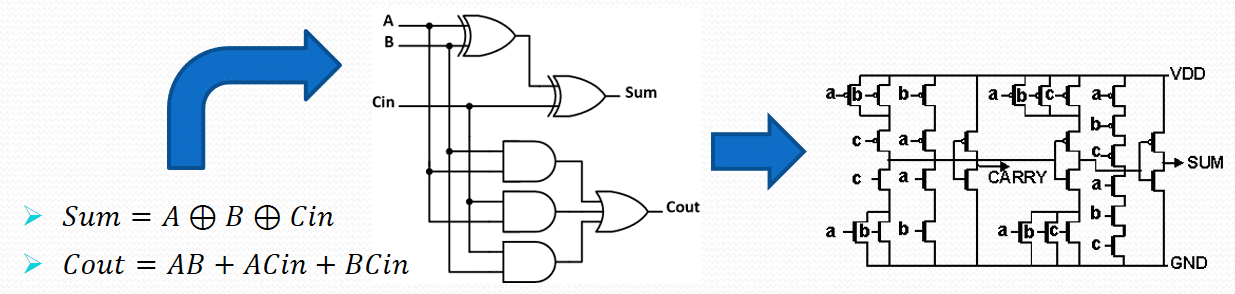

اکنون با مثالی که در تصویر زیر میبینید، این موضوع را بیشتر توضیح هم داد:

سنتز تمام جمعکننده از توصیف سطح بالا به توصیف سطح پایین

در برنامههای قبلی، راجع به تمام جمعکننده صحبت کردیم که تمام جمعکننده دارای سه ورودی A، B و Carry ورودی است و دو خروجی Sum و Carry خروجی را دارد.

در سمت چپ این تصویر توصیف جمعکنندهی کامل را به کمک دو عبارت منطقی میتوانید ببینید.

این یک سطح از توصیف است.

حالا ما میتوانیم همین جمعکنندهی کامل را به کمک گیتهای منطقی پایه به این صورت که در وسط شکل بالا میبینید، پیادهسازی بکنیم.

این هم یک توصیف از جمعکننده است، که توصیف سطح پایینتری نسبت به توصیف با عبارات منطقی است.

شما میدانید که هر گیت منطقی را در عمل در ICها به کمک مدارات ترانزیستوری پیادهسازی میکنند.

بنابراین اگر به ازای هر کدام از گیتهای منطقی این تمام جمعکننده، مدار معادل مدل ترانزیستوریاش را قرار بدهیم، میتوانیم به مدار ترانزیستوری که در سمت راست تصویر میبینید، برسیم.

این مدار هم در واقع بیان کنندهی یک جمعکننده است.

این مدار ترانزیستوری هم یک توصیف سطح پایینتر از همان جمع کنندهی اول است که به کمک توابع دیجیتالی نشان داده شد.

در اینجا ما از سه روش برای نمایش مفهوم جمعکنندهی کامل استفاده کردیم و از طرف دیگر دو مرحله سنتز انجام دادیم.

ابتدا سنتز از نمایش جمعکنندهی کامل با توابع منطقی به نمایش با گیتهای منطقی انجام شد.

بار دوم سنتز از نمایش جمعکنندهی کامل با توابع منطقی به نمایش جمعکننده با ترانزیستورها انجام شد.

حال مفهوم سنتز در FPGAها به چه معنا است؟

سنتز در FPGAها، پیادهسازی مدار توصیف شده به زبان، HDL به کمک منابع دیجیتالی موجود در FPGA است.

اجازه بدهید این موضوع را با مثال جمعکنندهی کامل توضیح بدهم.

جمعکنندهی کامل را میتوانیم به کمک زبان VHDL، همانطور که در برنامهی قبلی دیدیم، توصیف کنیم. اگر به یاد داشته باشید در بخش Architecture از علامت ارجاع (=>) برای توصیف جمعکننده استفاده میکردیم.

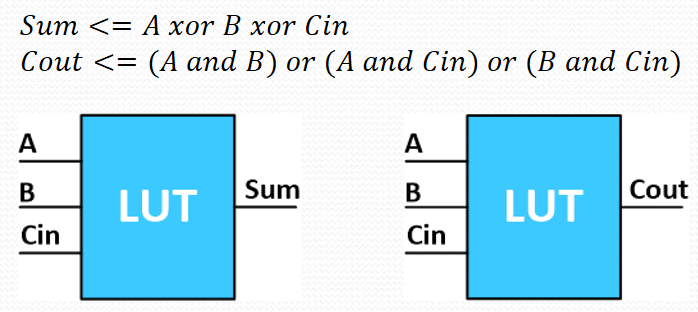

دو تابعی که در شکل زیر مشاهده میکنید دو عبارت هستند که به کمک گیتهای منطقی XOR،OR و ANDجمعکنندهی کامل را پیادهسازی میکنند.

پیادهسازی توابع منطقی در FPGA به کمک LUT

اما وقتی که این جمعکننده بخواهد درFPGA پیادهسازی شود، باید به کمک منابع دیجیتالی که در FPGA وجود دارند، پیادهسازی شود.

یکی از مهمترین منابع، همانطور که در برنامهی "FPGA چیست؟" در مورد آن صحبت کردیم، LUTها هستند.

بنابراین، ما میتوانیم به کمک یک LUT، خروجی Sum جمعکننده و به کمک LUT دیگر، خروجی Carry Out جمعکننده را مطابق شکل بالا پیادهسازی بکنیم.

۴ - جانمایی یا Placement

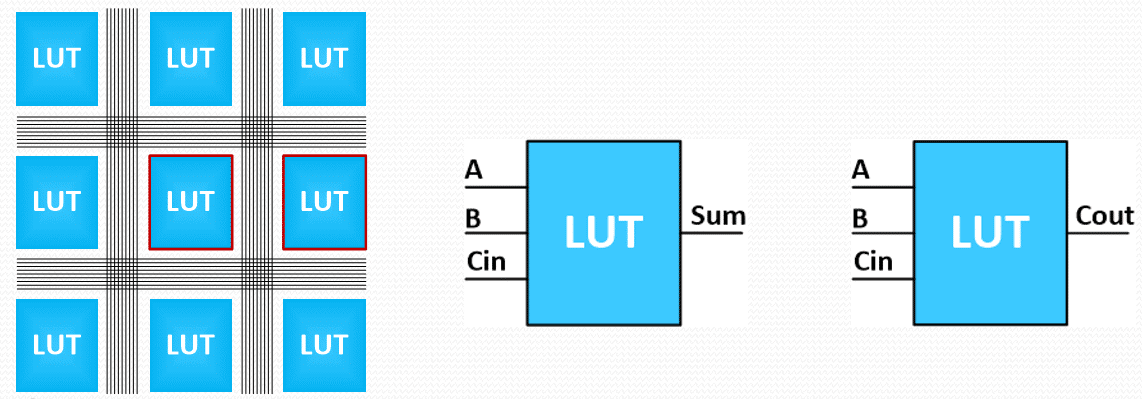

مرحلهی چهارم مرحلهی جانمایی یا Placement است.

در این مرحله مشخص میکنیم منابعی که در مرحلهی سنتز برای پیادهسازی طرح استفاده شده است، دقیقا در کجای FPGA قرار میگیرند.

مثلا در مورد مثال قبل، ما برای پیادهسازی جمعکنندهیکامل از دو LUT استفاده کردیم.

فرض کنیم در FPGAی که استفاده میکنیم ۴۰۰۰ LUT برای پیادهسازی مدار قرار داده شده است.

در مرحلهی جانمایی مشخص میشود که از میان این ۴۰۰۰ LUT، کدام دو LUT برای پیادهسازی جمعکننده استفاده میشود.

در مثال قبل من دو LUT که دور آن را با کادر قرمز مشخص کردهام، برای پیادهسازی این جمعکننده استفاده شده است.

پیادهسازی خروجی Sum و خروجی Carry Out با استفاده از LUT

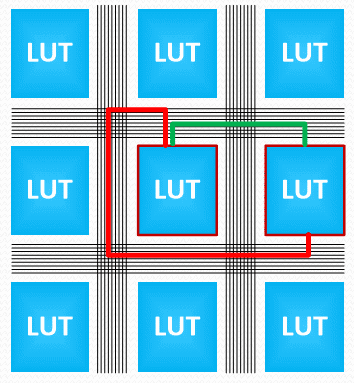

۵ - مسیریابی یا Routing

مرحلهی پنجم مرحلهی مسیریابی طرح یا Routing است.

همانطور که میدانید در FPGAها تعداد زیادی سیم وجود دارد که شما میتوانید با اتصال مناسب این سیمها به LUTها یا به یکدیگر، مدار موردنظرتان را تکمیل کنید.

همانطور که در زیر شکل میبینید دو LUT که برای پیادهسازی جمعکننده استفاده شده است را به کمک مسیر سبز رنگ، از طریق سیمهایی که از قبل در FPGA طراحی شده، به هم متصل کردیم.

Routing با استفاده از سیمهای درون FPGA

البته برای متصل کردن این دو LUT به هم، دهها و شاید صدها مسیر مختلف دیگر در این طرح وجود دارد. مثلا ما میتوانستیم از مسیر قرمز رنگ این دو LUT را به هم متصل کنیم.

اما اینکه دقیقا از چه مسیری این LUTها را به هم متصل کنیم به الگوریتمهای Routing و مسیریابی موجود در نرمافزارهای پیادهساز و معیارهایی که برای این مسئله وجود دارد، مربوط میشود.

یکی از این معیارها، انتخاب کوتاهترین مسیر بین منابع دیجیتالی است.

در این مورد در برنامههای بعدی بیشتر صحبت خواهیم کرد.

۶ - ایجاد فایل پیکرهبندی

مرحلهی ششم ایجاد فایل پیکرهبندی یا File Configuration است.

ما درمراحل قبلی، عمل سنتز، جانمایی و مسیریابی را انجام دادیم.

اما این مراحل باید به نحوی به FPGA منتقل شوند.

برای این کار نتایج حاصل از مراحل سنتز، جانمایی و مسیریابی درون یک فایل بیتی قرار داده میشود و این فایل بیتی بعد از اینکه به FPGA منتقل شد، باعث پیکرهبندی آن میشود.

اگر بخواهید بدانید که محتوای این فایل بیتی چیست، باید بگویم که محتوای این فایل بیتی در واقع تعیینکنندهی محتوای LUTها و سوییچهای مسیرها است.

به طوری که بعد از اینکه فایل بیتی به FPGA منتقل شد، FPGA به آن مداری که ما با کمک زبان HDL توصیف کردیم، تبدیل میشود.

۷ - پیکرهبندی FPGA

آخرین مرحله از مراحل پیادهسازی مدار به کمک FPGA، پیکرهبندی FPGA است.

همانطور که گفتم، حاصل تمام مراحل قبلی درون یک فایل بیتی که File Configuration نام دارد قرار میگیرد و سپس باید این فایل به FPGA منتقل شود.

برای انتقال این فایل به FPGA، از پروگرامر مخصوصی استفاده میشود.

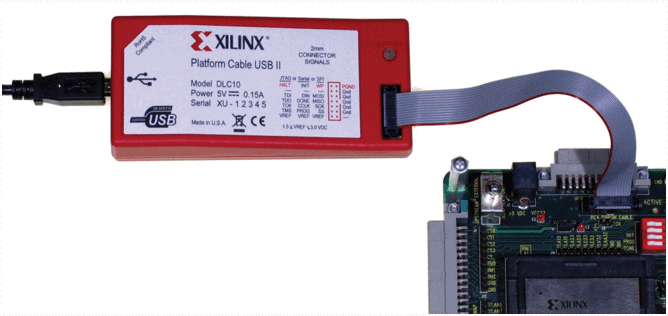

در شکل زیر میتوانید شکل پروگرامر مخصوص شرکت XILINX را ببینید.

پروگرامر مخصوص شرکت XILINX

این پروگرامر از یک سمت به کمک ارتباط USB به کامپیوتر متصل است و از طرف دیگر به کمک پروتکل JTag به FPGA متصل میشود.

فایل بیتی از طریق ارتباط USB به پروگرامر ارسال میشود و پروگرامر آن را از طریق پروتکل JTag به FPGA منتقل میکند.

در این مرحله FPGA تبدیل به مداری میشود که ما آن را به کمک کد توصیف سختافزاری طراحی کرده بودیم.

خوشبختانه تمام مراحل ذکر شده را میتوانید از طریق نرمافزارهای مخصوصی که برای این کار طراحی شده انجام دهید.

هر شرکتی که FPGA تولید میکند، نرمافزار مخصوصی هم برای انجام تمام این مراحل ساخته است.

مثلا در مورد شرکت XILINX نرمافزاری که تمام مراحل را انجام میدهد، نرمافزار ISE است، که شما به کمک این نرمافزار و بدون نیاز به هیچ نرمافزار دیگری میتوانید تمام این مراحل هفت گانه را انجام دهید.

وظایف طراح دیجیتال

اما سوالی که پیش میآید این است که با توجه به اینکه تمام این مراحل توسط نرمافزار انجام میشود، پس وظیفهی طراح دیجیتال چیست؟

شما برای طراحی دیجیتال چهار وظیفهی اصلی دارید:

۱ - نوشتن کد توصیف سختافزاری

اولین وظیفه نوشتن کد توصیف سختافزاری است که به کمک یکی از زبانهای VHDL یا Verilog این کار را انجام میدهید.

۲ - بررسی نتایج حاصل از سنتز، جانمایی و مسیریابی

مرحلهی دوم این است که نتایج حاصل از مراحل مهم سنتز، جانمایی و مسیریابی را بررسی کنید.

چون نرمافزار بعد از انجام هر کدام از این مراحل به شما گزارشهای مفصلی را ارائه میدهد و شما با بررسی این گزارشها میتوانید متوجه شوید که این مراحل به درستی انجام شده است یا خیر.

۳ - شبیهسازی

مرحلهی بعدی مرحلهی شبیهسازی است.

همانطور که گفتم شما بعد از انجام هر کدام از مراحل ورود طرح، سنتز، جانمایی و مسیریابی برای اینکه مطمئن باشید طرحتان درست کار میکند، باید شبیهسازی انجام دهید.

شبیهسازی و مقایسهی نتایج آن با نتایج مطلوب، یکی از مهمترین کارهای شما به عنوان پیادهساز دیجیتال است.

۴ - تست سیستم بعد از پیکرهبندی FPGA

آخرین کاری که برای پیادهسازی دیجیتال باید انجام دهید، تست سیستم بعد از پیکرهبندی FPGA است.

بعد از اینکه FPGA را پروگرام کردید و آن را تبدیل به مدار مورد نظرتان کردید، باید به کمک ابزارهایی که نرمافزار ISE در اختیارتان قرار میدهد طرحتان را بر روی FPGA تست کنید تا از صحت عملکرد آن در حین کار هم مطمئن شوید.آیا برنامه ویدئویی مراحل پیادهسازی مدار دیجیتال با FPGA برای شما مفید بود؟

لطفا نظرتان را در مورد این برنامه در پایین همین پست با دیگران به اشتراک بگذارید. همچنین با کلیک روی هر کدام از دکمههای اشتراک گذاری ابتدای این مطلب و به اشتراکگذاری آن در شبکههای اجتماعی میتوانید افراد بیشتری را در یادگیری این مطالب سهیم کنید.

با سلام

ممنون ااز زحماتتون

من حتی سایت های به زبان انگلیسی رو گشتم ولی به این شکل کامل و مرتب نبودند.

سلام،

خواهش میکنم. خوشحالم که مطالب سایت برای شما مفید بوده است.

موفق باشید.